### **SIAM LA 2021**

May 20, 2021

### Multiple Word Arithmetic with GPU Tensor Cores: Theory and Practice

#### Theo Mary

Sorbonne Université, CNRS, LIP6 https://www-pequan.lip6.fr/~tmary/

Slides available at <a href="https://bit.ly/la21multiword">https://bit.ly/la21multiword</a>

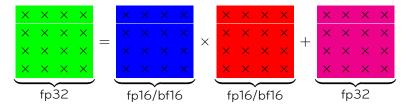

Joint work with Massimiliano Fasi (Örebro Univ.), Nicholas J. Higham, Mantas Mikaitis, Srikara Pranesh (Univ. Manchester), Florent Lopez (LSTC, Ansys). Tensor cores compute D = C + AB:

#### $fp32 \rightarrow fp16/bf16$ speedup evolution: P100: $2 \times$ V100: $8 \times$ A100: $16 \times$

Let  $A \in \mathbb{R}^{m \times n}$  and  $B \in \mathbb{R}^{n \times p}$  and compute C = AB. The computed  $\widehat{C}$  satisfies

$$\begin{split} |\widehat{C} - C| &\leq nu_{16}|A||B| & \text{in standard fp16/bf16 arithmetic} \\ |\widehat{C} - C| &\leq (2u_{16} + nu_{32})|A||B| & \text{with tensor cores} \\ |\widehat{C} - C| &\leq nu_{32}|A||B| & \text{in standard fp32 arithmetic} \end{split}$$

Blanchard, Higham, Lopez, M., Pranesh (2020) .

- Tensor cores greatly reduce the impact of error accumulation

- But error still depends on  $u_{16}$  because of the conversion of A and B

- $\Rightarrow\,$  Can we get rid of it to achieve an accuracy equivalent to fp32 ?

- Represent high precision number as the unevaluated sum of lower precision numbers

- Double-double arithmetic:

$$\mathbf{x} = \underbrace{\mathbf{x}_1}_{\mathsf{fp64}} + \underbrace{\mathbf{x}_2}_{\mathsf{fp64}}$$

- $\Rightarrow$  x has up to  $2 \times 53 = 106$  significand bits  $pprox 10^{-32}$  precision

- Less than fp128 (113 significand bits), but much faster, because computations rely on fp64 arithmetic

- Need for error-free transformations makes it much slower than fp64 ⇒ double-single arithmetic not meaningful on most processors

|          | Signif. bits | Exp. bits | Range         | Unit roundoff <i>u</i> |

|----------|--------------|-----------|---------------|------------------------|

| fp32     | 24           | 8         | $10^{\pm 38}$ | $6 \times 10^{-8}$     |

| fp16     | 11           | 5         | $10^{\pm 5}$  | $5 \times 10^{-4}$     |

| bfloat16 | 8            | 8         | $10^{\pm 38}$ | $4 \times 10^{-3}$     |

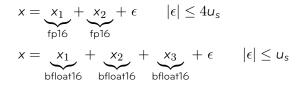

Let  $x \in \mathbb{R}$  and  $u_s = 2^{-24}$

# Double-half arithmetic with tensor cores

Apply this elementwise to  $A \in \mathbb{R}^{m \times n}$  and  $B \in \mathbb{R}^{n \times p}$ :

$$A = A_1 + A_2, \qquad B = B_1 + B_2$$

and compute C = AB as

$$C pprox \sum_{i,j} \mathsf{A}_i \mathsf{B}_j$$

using tensor cores

GPU tensor cores provide a new perspective:

- Intermediate computations are done in fp32 ⇒ no need for error-free transformations!

- Double-fp16  $\Rightarrow$  4× more flops (can be reduced to 3×)

- Triple-bfloat16  $\Rightarrow$  9× more flops (can be reduced to 6×)

- Tensor cores  $8 \times -16 \times$  faster than fp32

$\Rightarrow$  Multiword half arithmetic potentially faster at same accuracy!

Several recent papers around this idea:

- S. Markidis, S. W. D. Chien, E. Laure, I. B. Peng and J. S. Vetter, NVIDIA Tensor Core Programmability, Performance & Precision, IPDPSW 2018. Double-fp16 arithmetic for GEMM with Tensor Cores.

- A. Sorna, X. Cheng, E. D'Azevedo, K. Won and S. Tomov, Optimizing the Fast Fourier Transform Using Mixed Precision on Tensor Core Hardware, HiPCW 2018. Double-fp16 arithmetic for FFT with Tensor Cores.

- G. Henry, P. T. P. Tang and A. Heinecke, Leveraging the bfloat16 Artificial Intelligence Datatype For Higher-Precision Computations, ARITH 2019. Triple-bfloat16 arithmetic.

- D. Mukunoki, K. Ozaki, T. Ogita, T. Imamura, DGEMM Using Tensor Cores, and Its Accurate and Reproducible Versions, ISC 2020.

Double-fp16 arithmetic with Tensor and with fp64 target.

- Several others

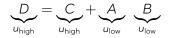

# Block FMA framework

We use the Block FMA framework from Blanchard et al. (2020) •  $A \in \mathbb{R}^{b_1 \times b}$ ,  $B \in \mathbb{R}^{b \times b_2}$ , and  $C \in \mathbb{R}^{b_1 \times b_2}$ ,

• Internal computation C + AB is done in precision  $u_{high}$

|               | $b_1$ | b   | $b_2$ | U <sub>low</sub> | <b>U</b> high |

|---------------|-------|-----|-------|------------------|---------------|

| Google TPU v1 | 256   | 256 | 256   | bfloat16         | fp32          |

| Google TPU v2 | 128   | 128 | 128   | bfloat16         | fp32          |

| NVIDIA Volta  | 4     | 4   | 4     | fp16             | fp32          |

| NVIDIA Ampere | 8     | 8   | 4     | fp16             | fp32          |

| NVIDIA Ampere | 8     | 8   | 4     | bfloat16         | fp32          |

| NVIDIA Ampere | 4     | 8   | 4     | tfloat32         | fp32          |

| Intel NNP-T   | 32    | 32  | 32    | bfloat16         | fp32          |

| Armv8-A       | 2     | 4   | 2     | bfloat16         | fp32          |

# General error analysis

For any  $x \in \mathbb{R}$  and p > 0, let

$$x_1 = \mathsf{fl}_{\mathsf{low}}(x)$$

$$x_2 = \mathsf{fl}_{\mathsf{low}}(x - x_1)$$

$$: x_{p} = \mathsf{fl}_{\mathsf{low}} \left( x - \sum_{i=1}^{p-1} x_{i} \right)$$

We obtain

$$x = \sum_{i=1}^{p} x_i + \Delta x, \quad |\Delta x| \le u_{\text{low}}^{p} |x|.$$

Using this representation elementwise on A and B:

:

$$A = \sum_{i=1}^{p} A_i + \Delta A, \quad |\Delta A| \leq u_{low}^{p} |A|,$$

$$B = \sum_{j=1}^{p} B_j + \Delta B, \quad |\Delta B| \leq u_{low}^{p} |B|.$$

Then the product C = AB is given by

$$C = \sum_{i=1}^{p} \sum_{j=1}^{p} A_{i}B_{j} + A \Delta B + \Delta A B - \Delta A \Delta B.$$

Compute the  $p^2$  products  $A_iB_j$  by chaining calls to the block FMA:

$$\widehat{C} = C + \Delta C, \quad |\Delta C| \le (n + p^2) u_{\mathsf{high}} |A| |B|.$$

Overall

$$\widehat{C} = AB + E, \quad |E| \leq \left(2u_{\mathsf{low}}^{p} + u_{\mathsf{low}}^{2p} + (n + p^{2})u_{\mathsf{high}}\right)|A||B|.$$

$x_k = fl_{low} \left( x - \sum_{i=1}^{k-1} x_i \right)$  is the approximation residual from the first k-1 words

$$\begin{split} |\mathsf{A}_i| &\leq u_{\mathsf{low}}^{i-1}(1+u_{\mathsf{low}})|\mathsf{A}| \\ |\mathsf{B}_j| &\leq u_{\mathsf{low}}^{j-1}(1+u_{\mathsf{low}})|\mathsf{B}| \\ |\mathsf{A}_i||\mathsf{B}_j| &\leq u_{\mathsf{low}}^{i+j-2}(1+u_{\mathsf{low}})^2|\mathsf{A}||\mathsf{B}| \end{split}$$

⇒ Not all  $p^2$  products  $A_i B_j$  need be computed! Skipping any product  $A_i B_j$  such that i + j > p + 1 yields  $\hat{C} = AB + E_i$ ,

$$|E| \le \left(2u_{\text{low}}^{p} + u_{\text{low}}^{2p} + (n+p^{2})u_{\text{high}} + \sum_{i=1}^{p-1} (p-i)u_{\text{low}}^{p+i-1} (1+u_{\text{low}})^{2}\right)|A||B|.$$

- number of products:  $p^2 \rightarrow p(p+1)/2$

- error to order  $u_{low}^p$ : constant  $2 \rightarrow p+1$

| U <sub>high</sub>       | Ulow                       |       | Error bound                                                                                 |

|-------------------------|----------------------------|-------|---------------------------------------------------------------------------------------------|

|                         | 2 <sup>-11</sup> (fp16)    |       | $\begin{array}{l} 2\times2^{-11}+n\times2^{-24}\\ n\times2^{-24} \end{array}$               |

| 2 <sup>-24</sup> (fp32) | 2 <sup>-8</sup> (bfloat16) | p = 2 | $2 \times 2^{-8} + n \times 2^{-24}  3 \times 2^{-16} + n \times 2^{-24}  n \times 2^{-24}$ |

Encompasses existing approaches and some new ones

### From theory to practice

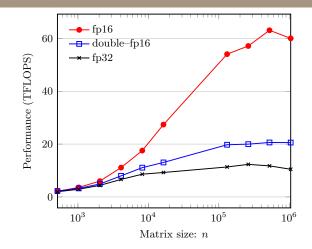

• Double-fp16 up to  $2\times$  faster than fp32

# From theory to practice

- Double-fp16 up to  $2\times$  faster than fp32

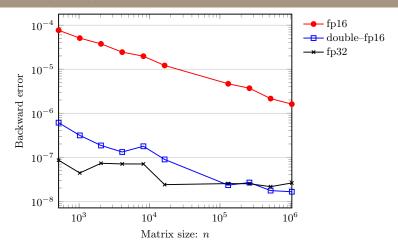

- Similar backward error for matrices with random [-1,1] uniform entries (decreasing error is expected B Higham and M. (2020) )

# From theory to practice

- Double-fp16 up to  $2\times$  faster than fp32

- Similar backward error for matrices with random [-1,1] uniform entries (decreasing error is expected B Higham and M. (2020) )

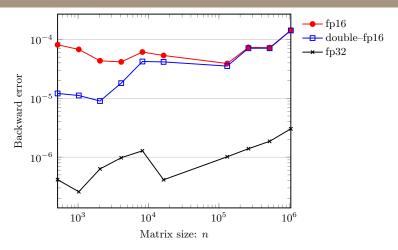

- [0,1] uniform entries!!

Our explanation: the culprit is round to zero (RZ)

- fp32 uses the standard RTN, but tensor cores only support RZ

Fasi, Higham, Mikaitis, Pranesh (2020)

- With data of nonzero mean and RZ, most rounding errors happen in the same direction

- ⇒ Worst-case bound  $nu_{32}$  is attained with RZ, whereas with RTN we can usually replace it by  $\sqrt{n}u_{32}$  🖹 Higham and M. (2019)

- Same error bound  $\neq$  same error !

# A proposed cure

- The worst-case accumulation bound  $nu_{32}$  is attained  $\Rightarrow$  need to reduce the bound

- FABsum 🖹 Blanchard, Higham, M. (2020)

- Sum blocks of size b in precision  $u_{32}$

- Combine n/b blocks in precision  $u_{64}$

- $\Rightarrow$  Reduced error bound  $bu_{32} + nu_{64}/b$

- Parameter *b* controls tradeoff between accuracy and performance

- FABsum with Tensor Cores: based on CUTLASS library, which implements uniform precision blocked summation ("splitK")

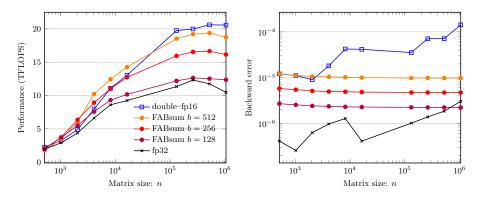

# A proposed cure (results)

- As fast as cuBLAS but an order of magnitude more accurate

- Almost as accurate as fp32 and slightly faster

- And anything in between: flexible tradeoff

# A proposed cure (results)

- As fast as cuBLAS but an order of magnitude more accurate

- Almost as accurate as fp32 and slightly faster

- And anything in between: flexible tradeoff

Thank you! Questions?